3.1.2 | THE FETCH DECODE EXECUTE CYCLE |

|

Topics from the Cambridge IGCSE (9-1) Computer Science 0984 syllabus 2023 - 2025.

|

OBJECTIVES

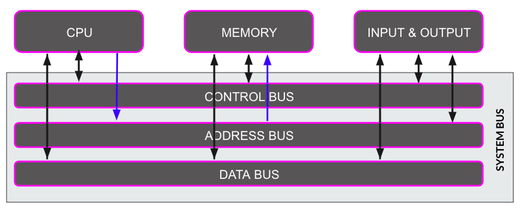

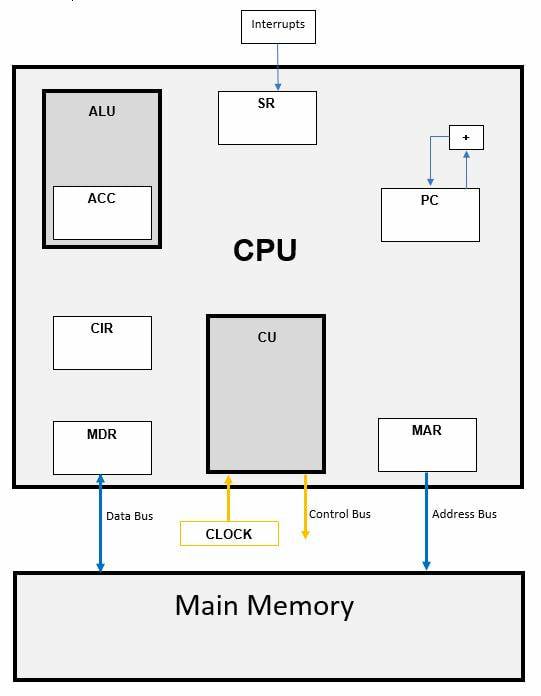

3.1.2(a) Understand the purpose of the components in a CPU, in a computer that has a Von Neumann architecture Including: – units: arithmetic logic unit (ALU) and control unit (CU) – registers: program counter (PC), memory address register (MAR), memory data register (MDR), current instruction register (CIR) and accumulator (ACC) – buses: address bus, data bus and control bus 3.1.2(b) Describe the process of the fetch–decode–execute cycle including the role of each component in the process. • How instructions and data are fetched from random access memory (RAM) into the CPU, how they are processed using each component and how they are then executed • Storing data and addresses into specific registers • Using buses to transmit data, addresses and signals • Using units to fetch, decode and execute data and instructions |

ALSO IN THIS TOPIC

3.1.1 COMPUTER ARCHITECTURE YOU ARE HERE | 3.1.2 COMPUTER ARCHITECTURE 3.1.3 COMPUTER ARCHITECTURE 3.1.4 COMPUTER ARCHITECTURE(CIE) 3.1.5 COMPUTER ARCHITECTURE 3.2.1 INPUT AND OUTPUT DEVICES 3.2.2 INPUT AND OUTPUT DEVICES 3.2.3 INPUT AND OUTPUT DEVICES 3.3 DATA STORAGE 3.4 NETWORK HARDWARE REVISION CARDS TOPIC 3 KEY TERMINOLOGY TOPIC 3 ANSWERS TOPIC 3 TEACHER RESOURCES TOPIC 1 TEACHER RESOURCES (CIE) |